Difference between revisions of "DPS921/Group 8"

(→Padding) |

(→Padding) |

||

| Line 23: | Line 23: | ||

[[File:Cacheline1.jpeg]] | [[File:Cacheline1.jpeg]] | ||

| + | |||

| + | [[File:Cacheline2.jpeg]] | ||

== Synchronization == | == Synchronization == | ||

=Conclusion = | =Conclusion = | ||

Revision as of 23:57, 25 November 2018

Contents

Group 8

Our Project: Analyzing False Sharing - Case Studies

Group Members

False Sharing in Parallel Programming

Introduction

Location of the problem - Local cache

Signs of false sharing

Solutions

Padding

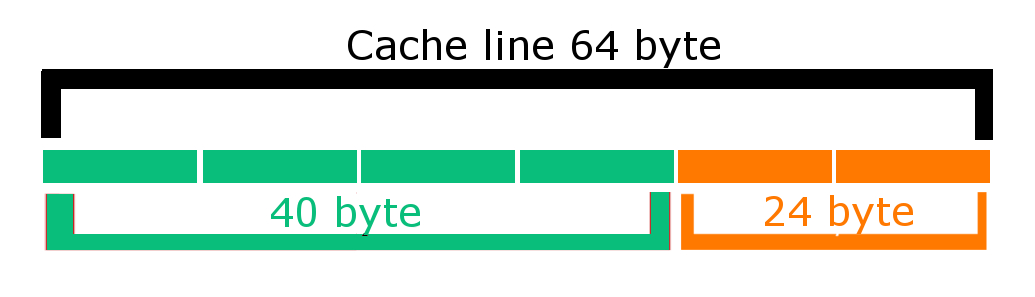

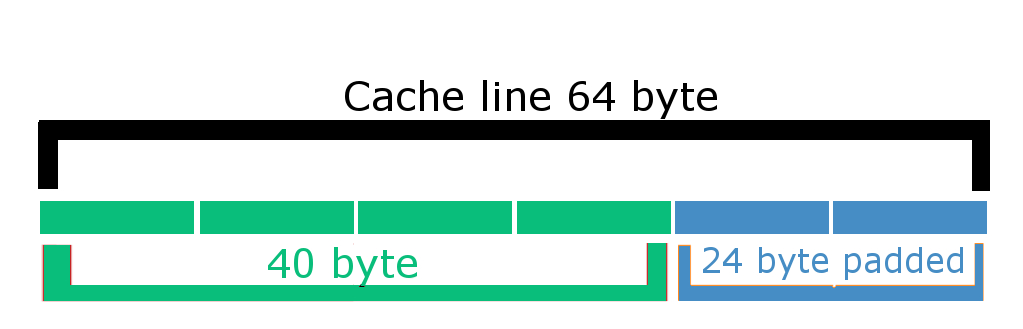

One way to eliminating false sharing is to add in padding to the data. The idea of padding in general is for memory alignment, by utilizing padding we can eliminate cache line invalidation interfering with read and write of elements.

How padding works: Let's say we have an int element num[i] = 10; in memory this would be stored as 40 bytes ( 10 * 4 byte) and a single standard cache line is 64 byte which means 24 byte needs to be padded otherwise another element will occupy that region which will result in 2 or more thread accessing same cache line causing false sharing.